MicroChemicals

# FURTHER PROCESSING OF SILICON WAFERS: ${\rm SIO}_{2'}\,{\rm SI}_{3}{\rm N}_{4'}$ METALLIZATION, EPITAXY AND DICING

The previous chapter described the process steps from quartz sand to silicon wafers manufactured for photolithography. Often, however, prior to the start of the further structuring, the wafers go through certain process steps such as, for example, thermal oxidation or coating with metals or dielectrics as described in this chapter.

# **Thermal Oxidation**

#### Areas of Application

The electronic (resistivity  $10^{14} - 10^{16}$  ohm cm, dielectric strength  $10^6 - 10^7$  V/cm, barrier for electrons and holes > 3 eV), mechanical (melting point approx. 1700 °C) and optical (transparent in the visible as well as near infrared and ultraviolet spectral range) properties of SiO<sub>2</sub> make it a suitable material for a multiple range of use:

As dielectric film in transistors, capacitors (DRAM) or flash-memories, as a hard mask for diffusion, implantation, wet or dry chemical etching; and generally as an isolator between integrated devices, or as an anti-reflective layer on e.g. solar cells.

Required  $SiO_2$  film thicknesses range from a few nm (gate-oxide of state-of-the-art CMOS transistors) up to several µm for electrical insulation between components.

#### **Oxidation Technique**

Compared to (crystalline) quartz, native (= few nm grown at room temperature in air) and thermal (growth temperature 800 - 1200°C) silicon dioxide (schema of an oxidation Fig. 24) is amorphous (= without long-range atomic lattice order).

The silicon in native or thermally grown  $SiO_2$  evolves from the Si substrate, which is partially consumed during  $SiO_2$  growth: The growth of 100 nm  $SiO_2$  requires approx. 46 nm Si, while the total wafer thickness simultaneously increases by approx. 54 nm.

A distinction is made between *dry oxide*  $(Si + O_2 \rightarrow SiO_2)$  and - with H<sub>2</sub>O as a process gas - *wet oxide*  $(Si + 2 H_2O \rightarrow SiO_2 + 2 H_2)$ . At the same process parameters, due to the higher growth rate, wet oxide reveals a higher porosity and HF etch rate.

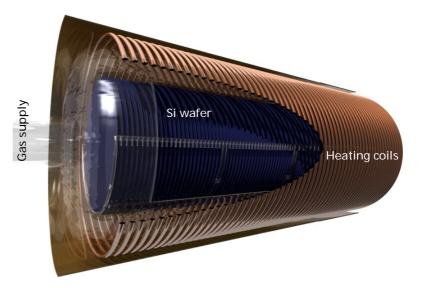

Fig. 24: Diagram of an oxidation furnace for Si wafers

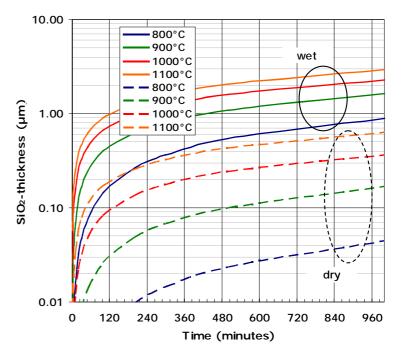

Fig. 25: The attained film thicknesses of wet and dry (dashed)  $SiO_2$  as a function of the  $SiO_2$  growth time and temperature.

## Oxidation Rate and Attainable SiO<sub>2</sub> Film Thickness

At the beginning of thermal  $SiO_2$  growth, the chemical reactions on the surface/interface limit the film thickness which increases linearly with time. With the  $SiO_2$  thickness increasing, the more and more dominating oxygen diffusion through the already-grown film towards the  $Si/SiO_2$  interface limits the growth rate. The  $SiO_2$  thickness now increases with the square-root of growth time.

Besides the process gas composition  $(O_2/H_2O)$ , their partial pressure as well as the substrate temperature (activation energy of oxygen diffusion and chemical reaction at the Si/SiO<sub>2</sub> interface), the SiO<sub>2</sub> growth rate also depends on the Si substrate crystal orientation, mechanical strain of the substrate (e.g. in case of already processed device layers), as well as on substrate doping (e.g. faster oxide growth on phosphorous doped silicon).

# PECVD of SiO<sub>2</sub>

#### Mechanism

As an alternative to thermal oxidation of silicon,  $SiO_2$  layers can also be deposited on silicon from the gas phase (PECVD = <u>Plasma Enhanced Chemical Vapour Deposition</u>) via

$$SiH_4 + 2 N_2O \rightarrow SiO_2 + 2 N_2.$$

## Advantages over Thermal SiO<sub>2</sub>

Since the film thickness during the PECVD deposition increases linearly over time, very thick layers consisting of several  $\mu$ m can be grown significantly faster than via thermal oxidation. If only a few wafers are to be coated, the PECVD deposition is more favourable than the thermal oxidation process, where larger numbers (e.g. 100 wafers) can be processed simultaneously.

Thermal SiO<sub>2</sub> always contains the impurities (dopants) of the silicon substrate, while the composition of SiO<sub>2</sub> layers grown by PECVD is independent of the substrate.

## Disadvantages over Thermal SiO<sub>2</sub>

PECVD SiO<sub>2</sub> grows more amorphously with lots of pinholes than a thermal oxide, affecting the electrical and chemical properties:

Compared to thermal  $SiO_2$ , PECVD  $SiO_2$  has a lower electrical breakdown strength, which is why the gate oxides, which are, in some cases, only a few nm thick, are preferably produced thermally.

The wet chemical etching rate of PECVD  $SiO_2$  is also significantly higher than that of thermal oxide, which is why it is not well suitable as an etching mask, for example, for anisotropic Si etching.

# Deposition of Silicon Nitride

## Use of Silicon Nitride

In the field of toolmaking, stoichiometric silicon nitride  $(Si_3N_4)$  with its very high mechanical and thermal stability is used for tools such as roller bearings used under harsh conditions. For semiconductor devices, the chemical, electrical and optical properties of amorphous hydrogenated silicon nitride  $(SiN_x)$  make this material well-suited for different applications, such as for passivation or insulating layers in integrated circuits masking or etch stop material in wet and plasma etching processes due to its high chemical stability masking material in silicon oxidation processes due to the very low oxygen diffusion coefficient in  $SiN_x$  anti-reflective coating in photovoltaics due to its adjustable refractive index.

## PECVD Silicon Nitride

The amorphous silicon nitride (SiN<sub>x</sub>) deposited using PECVD (*Plasma Enhanced Chemical Vapour Deposition*) from SiH<sub>4</sub> and NH<sub>3</sub>, depending on the deposition temperature and gas composition, typically contains 5 - 20 atom% hydrogen (thus sometimes called SiN<sub>x</sub>:H) which saturates dangling bonds and thus chemically and mechanically stabilises the SiN<sub>x</sub> lattice.

$SiN_x$  can be etched via photoresist masks either with buffered or unbuffered HF or (selectively to SiO<sub>2</sub>) with hot concentrated phosphoric acid. The HF etch rate of  $SiN_x$  depends on the  $SiN_x$  deposition temperature and its refractive index.

A hydrogen-rich SiN<sub>x</sub> film deposited at 100°C with a refractive index of n = 1.9 shows an etch rate of several 100 nm/min in buffered HF (12.5 % HF). The etch rate drops to less than 10 nm/min for SiN<sub>x</sub> films deposited at 400°C with a refractive index of n = 2.

#### LPCVD Silicon Nitride

LPCVD (Low Pressure Chemical Vapour Deposition) Silicon nitride is deposited via

$$3 \operatorname{SiH}_2\operatorname{Cl}_2 + 4 \operatorname{NH}_3 \rightarrow \operatorname{Si}_3\operatorname{N}_4 + 6 \operatorname{HCI} + 6 \operatorname{H}_2$$

at significantly higher temperatures of around 700 - 850°C compared with the PECVD deposition. As a result, the layer is significantly lower in hydrogen and more stoichiometric than PECVD nitride and exhibits both very good electrical properties and edge coverage, high thermal stability and a low etching rate in hydrofluoric acid.

The deposition takes place via the sub-steps 1) gas supply of the reactants, 2) physical bonding of the molecules on the surface, 3) chemical bonding on the surface and 4) desorption and removal of the byproducts. The growth rate is limited almost exclusively by the chemical reaction on the growing layer and not

by the supply and consumption of the raw materials. Significant depletion of the reactants is not attained by the lower growth rate compared to the PECVD deposition. Therefore many (such as 25 or 50) wafers can be simultaneously processed in the gas stream of a reactor with very high film thickness homogeneity on the wafer surface and from wafer to wafer in a batch.

The deposition can be controlled so that either mechanically and ideally low stress or nearly stoichiometric  $(SI_3N_4)$  silicon nitride is produced.

Material Properties of Silicon Nitride

and Silicon Dioxide

**MicroChemicals**

Fig. 26: A LPCVD reactor (left) and  $\rm Si_3N_4$  coated Si wafers (right). Both images kindly provided by IMSAS, University of Bremen.

| Material                                               | Thermal expansion coe <b>ffi</b> cient (10%/ K) | Refractive index ( <b>λ</b> =<br>600 nm) | Dielectric strength<br>(kV/mm) | strength Density<br>(g/cm³) |  |

|--------------------------------------------------------|-------------------------------------------------|------------------------------------------|--------------------------------|-----------------------------|--|

| PECVD SIO <sub>2</sub>                                 |                                                 | 1.45 - 1.47                              | 600 - 700                      |                             |  |

| SiO <sub>2</sub> (mono-crystal-<br>line)               | 7.5 - 14                                        | 1.54                                     | > 1000                         | 2.65                        |  |

| PECVD SIN <sub>x</sub>                                 |                                                 | > 2.01*                                  | 600 - 700                      |                             |  |

| LPCVD SIN <sub>x</sub>                                 |                                                 | 2.01 - 2.05*                             | > 1000                         |                             |  |

| SI <sub>3</sub> N <sub>4</sub> (mono-crystal-<br>line) | 3.3                                             | 2.01                                     | > 1000                         | 3.29                        |  |

Table 1: A comparison of the material properties of silicon nitride and silicon oxide

\*The refractive index increases with Si-rich deposits

# Metallisation

Surface metallisation of wafers is usually done by thermal evaporation or sputtering. Since the adhesion of many metals to silicon is comparatively poor, it is sometimes advisable to use a 10 - 20 nm chrome or titanium metallic adhesion layer between the substrate and the actual metallisation if the process allows for it. In the case of a subsequent coating of the metal film with photoresist, it should be noted that this usually results in a very poor adhesion on noble metals. Accordingly, a further adhesion layer of 10-20 nm

chromium or titanium film between the noble metal and the resist can make sense.

## Epitaxy

#### Mechanism

In wafer fabrication, silicon epitaxy refers to the growth of a thin layer of single-crystalline silicon onto a single-crystalline silicon substrate, usually via chemical vapour deposition. Commonly used process gases are silicon tetrachloride (SiCl<sub>4</sub>), dichlorsilan (SiH<sub>2</sub>Cl<sub>2</sub>), trichlorosilane (SiHCl<sub>3</sub>) or silane (SiH<sub>4</sub>), mixed with hydrogen, which are thermally decomposed to silicon on the surface of wafers heated up to typically 600 - 1000°C. The Si atoms released from the gaseous compounds form mono-crystalline silicon monolayer by monolayer on the silicon substrate.

#### **Application Areas**

The addition of dopants such as phosphine, arsine or diborane to the process gas allows the realisation of certain doping profiles in the epitaxial film which is required for, e.g. box-shaped doped structures or a low-doped layer on top of highly doped silicon which cannot be realised by diffusion.

Already realised films such as areas doped via ion implantation, or microelectronic devices can be buried under an epitaxial layer (*buried layer*).

Since the oxygen and carbon impurity concentrations in epitaxial layers are very low, the electronic quality of this film is better than for the silicon substrate underneath, which can be important for integrated devices.

# **SOI** Wafers

#### Principle

SOI (*Silicon On Insulator*) wafers are wafers with a crystalline silicon film or devices lithographically made from this film located on an electrical insulator such as SiO2. There are two main fields of application for SOI wafers:

#### **Application Areas**

Transistors located on an electrically insulating film have a lower capacity and smaller electrical current leakage as compared to transistors directly sitting on the silicon substrate. Therefore, the transistors can be packed more densely, their energy consumption is lower, and the switching speed increased which allows higher clock rates and lower power demand.

In micro-optics, the insulating film allows integrated optical components including waveguides in which  $\mu$ m waves can be guided in silicon (refractive index = 3.5) embedded in SiO<sub>2</sub> (refractive index = 1.5) by total reflection.

## Technique

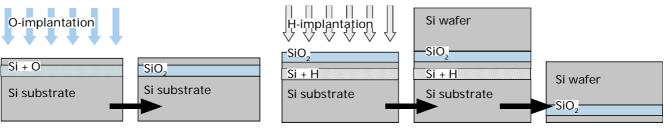

One technique for producing SOI wafers is the SIMOX<sup>TM</sup> process (*Separation by Implantation of Oxygen*, Fig. 27), starting with oxygen implantation in silicon wafers, which allows an accurate control of the depth profile of the implanted O-atoms (described in more detail in Chapter 29 on page 131). Subsequently, a high temperature step forms the SiO<sub>2</sub> layer where the O-atoms have been captured in the silicon lattice,

Fig. 27: One technique for producing SOI wafers is the SIMOX<sup>TM</sup> process (Separation by IMplantation of OXgen) Fig. 28: Another possibility of manufacturing SOI wafers via the *Smart Cut* technique combines hydrogen ion implantation and wafer bond-ing.

and simultaneously thermally anneals the crystal structure of the silicon above distorted by the implantation process.

The Smart-Cut<sup>TM</sup> technique (Fig. 28) combines hydrogen ion implantation and wafer bonding. Hydrogen ions are implanted in an oxidized silicon wafer. This wafer is bonded with another wafer without SiO<sub>2</sub> layer, hereby completely and permanently bonded to each other. This wafer bonding is carried out either by high mechanical pressure with the aid of hydrogen bonds and Van der Waals interactions or by means of anodic bonding in which the formation of chemical bonds is induced by applying an electrical voltage to the contact surface of both wafers.

A baking step (> 500°C) splits the oxidized wafer along the depth of the implanted hydrogen atoms induced by mechanical stress.

# Dicing of Wafers

#### Principle

Wafer dicing allows to cut rectangular pieces from circular wafers. Dicing can be accomplished by scribing and breaking, by mechanical sawing (using a blade or wire saw), or by laser cutting. The material of the substrate and the size of the diced pieces are limited less from technical than by economic boundaries: A dicing often only makes sense starting from 25 output wafers due to the relatively high set-up costs.

Realisable Parameters for Isolated Si Wafers Which We Can Supply

Material:CZ-Si or FZ-Si, optionally with thermal  $SiO_2$ Dimensions:From 5 x 5 mm to 120 x 100 mmWafer thickness:200  $\mu$ m - 1 mmOrientation:<100> or <111>; <110> on request

#### **Our Photoresists: Application Areas and Compatibilities**

|                                  | Recommended Applications <sup>1</sup>                                                                     | Resist Family                                          | Photoresists                                                                                                             | Resist Film<br>Thickness <sup>2</sup>                          | Recommended Developers <sup>3</sup>                                                                                                                                                                                        | Recommended Re-<br>movers <sup>4</sup>                                                                                               |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

|                                  |                                                                                                           | AZ <sup>®</sup> 1500                                   | AZ <sup>®</sup> 1505<br>AZ <sup>®</sup> 1512 HS<br>AZ <sup>®</sup> 1514 H<br>AZ <sup>®</sup> 1518                        | ≈ 0.5 µm<br>≈ 1.0 - 1.5 µm<br>≈ 1.2 - 2.0 µm<br>≈ 1.5 - 2.5 µm | AZ <sup>®</sup> 351B, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF, AZ <sup>®</sup> Developer                                                                                                                          |                                                                                                                                      |  |

|                                  | Improved adhesion for wet etching, no                                                                     | AZ <sup>®</sup> 4500                                   | AZ <sup>®</sup> 4533<br>AZ <sup>®</sup> 4562                                                                             | ≈ 3 - 5 µm<br>≈ 5 - 10 µm                                      | ≈ 3 - 5 µm A 78 400K A 78 200 MIE A 78 700 MIE A 78 2000 MIE                                                                                                                                                               |                                                                                                                                      |  |

| Positive                         | focus on steep resist sidewalls                                                                           | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | AZ <sup>®</sup> 400K, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF, AZ <sup>®</sup> 2026 MIF                         | AZ <sup>®</sup> 100 Remover,                                   |                                                                                                                                                                                                                            |                                                                                                                                      |  |

| Pos                              | Spray coating                                                                                             | AZ <sup>®</sup> PL 177<br>AZ <sup>®</sup> 4999         | AZ <sup>®</sup> PL 177                                                                                                   | ≈ 3 - 8 µm<br>≈ 1 - 15 µm                                      | AZ <sup>®</sup> 351B, AZ <sup>®</sup> 400K, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF, AZ <sup>®</sup> 2026 MIF<br>AZ <sup>®</sup> 400K, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF, AZ <sup>®</sup> 2026 MIF | TechniStrip <sup>®</sup> P1316<br>TechniStrip <sup>®</sup> P1331                                                                     |  |

| _                                | Dip coating                                                                                               | MC Dip Coating F                                       | Resist                                                                                                                   |                                                                | $AZ^{\text{B}}$ 351B, $AZ^{\text{B}}$ 400K, $AZ^{\text{B}}$ 326 MIF, $AZ^{\text{B}}$ 726 MIF, $AZ^{\text{B}}$ 2026 MIF                                                                                                     | -                                                                                                                                    |  |

|                                  | Steep resist sidewalls, high resolution<br>and aspect ratio for e. g. dry etching or                      | AZ <sup>®</sup> ECI 3000                               | AZ <sup>®</sup> ECI 3007<br>AZ <sup>®</sup> ECI 3012<br>AZ <sup>®</sup> ECI 3027                                         | ≈ 0.7 μm<br>≈ 1.0 - 1.5 μm<br>≈ 2 - 4 μm                       | AZ <sup>®</sup> 351B, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF, AZ <sup>®</sup> Developer                                                                                                                          |                                                                                                                                      |  |

|                                  | plating                                                                                                   | AZ <sup>®</sup> 9200                                   | AZ <sup>®</sup> 9245<br>AZ <sup>®</sup> 9260                                                                             | ≈ 3 - 6 µm<br>≈ 5 - 20 µm                                      | AZ <sup>®</sup> 400K, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF                                                                                                                                                     |                                                                                                                                      |  |

|                                  | Elevated thermal softening point and high resolution for e.g. dry etching                                 | AZ <sup>®</sup> 701 MiR                                | AZ <sup>®</sup> 701 MiR (14 cPs)<br>AZ <sup>®</sup> 701 MiR (29 cPs)                                                     | ≈ 0.8 µm<br>≈ 2 - 3 µm                                         |                                                                                                                                                                                                                            |                                                                                                                                      |  |

| Positive<br>(chem.<br>amplified) | Steep resist sidewalls, high resolution<br>and aspect ratio for e. g. dry etching or<br>plating           | AZ <sup>®</sup> XT                                     | AZ <sup>®</sup> 12 XT-20PL-05<br>AZ <sup>®</sup> 12 XT-20PL-10<br>AZ <sup>®</sup> 12 XT-20PL-20<br>AZ <sup>®</sup> 40 XT | ≈ 3 - 5 μm<br>≈ 6 - 10 μm<br>≈ 10 - 30 μm<br>≈ 15 - 50 μm      |                                                                                                                                                                                                                            | AZ <sup>®</sup> 100 Remover,<br>TechniStrip <sup>®</sup> P1316<br>TechniStrip <sup>®</sup> P1331                                     |  |

| a a                              |                                                                                                           | AZ <sup>®</sup> IPS 6050                               |                                                                                                                          | ≈ 20 - 100 µm                                                  |                                                                                                                                                                                                                            |                                                                                                                                      |  |

| Image<br>Re-<br>versal           | Elevated thermal softening point and                                                                      | AZ <sup>®</sup> 5200                                   | AZ <sup>®</sup> 5209<br>AZ <sup>®</sup> 5214                                                                             | ≈ 1 µm<br>≈ 1 - 2 µm                                           | AZ <sup>®</sup> 351B, AZ <sup>®</sup> 326 MIF, AZ <sup>®</sup> 726 MIF                                                                                                                                                     | TechniStrip <sup>®</sup> Micro D2<br>TechniStrip <sup>®</sup> P1316                                                                  |  |

| R R                              | undercut for lift-off applications                                                                        | ті                                                     | TI 35ESX<br>TI xLift-X                                                                                                   | ≈ 3 - 4 µm<br>≈ 4 - 8 µm                                       | AZ 3310, AZ 320 WIF, AZ 720 WIF                                                                                                                                                                                            | TechniStrip <sup>®</sup> P1331                                                                                                       |  |

| -                                | Negative resist sidewalls in combination with no thermal softening for lift-off                           | AZ <sup>®</sup> nLOF 2000                              | AZ <sup>®</sup> nLOF 2020<br>AZ <sup>®</sup> nLOF 2035<br>AZ <sup>®</sup> nLOF 2070                                      | ≈ 1.5 - 3 μm<br>≈ 3 - 5 μm<br>≈ 6 - 15 μm                      |                                                                                                                                                                                                                            | TechniStrip <sup>®</sup> NI555                                                                                                       |  |

| re<br>king                       | application                                                                                               | AZ <sup>®</sup> nLOF 5500                              | AZ <sup>®</sup> nLOF 5510                                                                                                | ≈ 0.7 - 1.5 µm                                                 |                                                                                                                                                                                                                            | TechniStrip <sup>®</sup> NI555<br>TechniStrip <sup>®</sup> NF52<br>TechniStrip <sup>®</sup> MLO 07                                   |  |

| Negative<br>(Cross-linking)      |                                                                                                           |                                                        | AZ <sup>®</sup> 15 nXT (115 cPs)<br>AZ <sup>®</sup> 15 nXT (450 cPs)                                                     | ≈ 2 - 3 µm<br>≈ 5 - 20 µm                                      | $AZ^{\otimes}$ 326 MIF, $AZ^{\otimes}$ 726 MIF, $AZ^{\otimes}$ 2026 MIF                                                                                                                                                    | _ recnniStrip* MLO 07                                                                                                                |  |

| Cro                              | Improved adhesion, steep resist side-<br>walls and high aspect ratios for e. g. dry<br>etching or plating | AZ <sup>®</sup> nXT                                    | AZ <sup>®</sup> 125 nXT                                                                                                  | ≈ 20 - 100 µm                                                  | $AZ^{\otimes}$ 326 MIF, $AZ^{\otimes}$ 726 MIF, $AZ^{\otimes}$ 2026 MIF                                                                                                                                                    | TechniStrip <sup>®</sup> P1316<br>TechniStrip <sup>®</sup> P1331<br>TechniStrip <sup>®</sup> NF52<br>TechniStrip <sup>®</sup> MLO 07 |  |

#### **Our Developers: Application Areas and Compatibilities**

#### **Inorganic Developers**

(typical demand under standard conditions approx. 20 L developer per L photoresist)

AZ<sup>®</sup> Developer is based on sodium phosphate and -metasilicate, is optimized for minimal aluminum attack and is typically used diluted 1 : 1 in DI water for high contrast or undiluted for high development rates. The dark erosion of this developer is slightly higher compared to other developers.

AZ<sup>®</sup> 351B is based on buffered NaOH and typically used diluted 1:4 with water, for thick resists up to 1:3 if a lower contrast can be tolerated.

AZ<sup>®</sup> 400K is based on buffered KOH and typically used diluted 1:4 with water, for thick resists up to 1:3 if a lower contrast can be tolerated.

AZ<sup>®</sup> 303 specifically for the AZ® 111 XFS photoresist based on KOH / NaOH is typically diluted 1:3-1:7 with water, depending on whether a high development rate, or a high contrast is required

#### Metal Ion Free (TMAH-based) Developers

(typical demand under standard conditions approx. 5 - 10 L developer concentrate per L photoresist)

AZ<sup>®</sup> 326 MIF is 2.38 % TMAH- (TetraMethylAmmoniumHydroxide) in water.

AZ® 726 MIF is 2.38 % TMAH- (TetraMethylAmmoniumHydroxide) in water, with additional surfactants for rapid and uniform wetting of the substrate (e. g. for puddle development)

AZ<sup>®</sup> 826 MIF is 2.38 % TMAH- (<u>TetraMethylAmmoniumHydroxide</u>) in water, with additional surfactants for rapid and uniform wetting of the substrate (e. g. for puddle development) and other additives for the removal of poorly soluble resist components (residues with specific resist families), however at the expense of a slightly higher dark erosion.

#### **Our Removers: Application Areas and Compatibilities**

AZ<sup>®</sup> 100 Remover is an amine solvent mixture and standard remover for AZ<sup>®</sup> and TI photoresists. To improve its performance, AZ<sup>®</sup> 100 remover can be heated to 60 - 80°C. Because the AZ<sup>®</sup> 100 Remover reacts highly alkaline with water, it is suitable for this with respect to sensitive substrate materials such as Cu, Al or ITO only if contamination with water can be ruled out.

**TechniStrip<sup>®</sup> P1316** is a remover with very strong stripping power for Novolak-based resists (including all AZ<sup>®</sup> positive resists), epoxy-based coatings, polyimides and dry films. At typical application temperatures around 75°C, TechniStrip<sup>®</sup> P1316 may dissolve cross-linked resists without residue also, e.g. through dry etching or ion implantation. TechniStrip<sup>®</sup> P1316 can also be used in spraying processes. For alkaline sensitive materials, TechniStrip<sup>®</sup> P1331 would be an alternative to the P1316. Not compatible with Au.

TechniStrip® P1331 can be an alternative for TechniStrip® P1316 in case of alkaline sensitive materials. TechniStrip® P1331 is not compatible with Au.

**TechniStrip**<sup>®</sup> NI555 is a stripper with very strong dissolving power for Novolak-based negative resists such as the AZ<sup>®</sup> 15 nXT and AZ<sup>®</sup> nLOF 2000 series and very thick positive resists such as the AZ<sup>®</sup> 40 XT. TechniStrip<sup>®</sup> NI555 was developed not only to peel cross-linked resists, but also to dissolve them without residues. This prevents contamination of the basin and filter by resist particles and skins, as can occur with standard strippers. TechniStrip<sup>®</sup> NI555 is not compatible with GaAs.

TechniClean<sup>TM</sup> CA25 is a semi-aqueous proprietary blend formulated to address post etch residue (PER) removal for all interconnect and technology nodes. Extremely efficient at quickly and selectively removing organo-metal oxides from AI, Cu, Ti, TiN, W and Ni.

TechniStrip<sup>™</sup> NF52 is a highly effective remover for negative resists (liquid resists as well as dry films). The intrinsic nature of the additives and solvent make the blend totally compatible with metals used throughout the BEOL interconnects to WLP bumping applications.

TechniStrip<sup>™</sup> Micro D2 is a versatile stripper dedicated to address resin lift-off and dissolution on negative and positive tone resist. The organic mixture blend has the particularity to offer high metal and material compatibility allowing to be used on all stacks and particularly on fragile III/V substrates for instance.

TechniStrip<sup>™</sup> MLO 07 is a highly efficient positive and negative tone photoresist remover used for IR, III/V, MEMS, Photonic, TSV mask, solder bumping and hard disk stripping applications. Developed to address high dissolution performance and high material compatibility on Cu, Al, Sn/Ag, Alumina and common organic substrates.

#### **Our Wafers and their Specifications**

#### Silicon-, Quartz-, Fused Silica and Glass Wafers

Silicon wafers are either produced via the Czochralski- (CZ-) or Float zone- (FZ-) method. The more expensive FZ wafers are primarily reasonable if very high-ohmic wafers (> 100 Ohm cm) are required.

Quartz wafers are made of monocrystalline SiO<sub>2</sub>, main criterion is the crystal orientation (e. g. X-, Y-, Z-, AT- or ST-cut)

Fused silica wafers consist of amorphous SiO<sub>2</sub>. The so-called JGS2 wafers have a high transmission in the range of ≈ 280 - 2000 nm wavelength, the more expensive JGS1 wafers at ≈ 220 - 1100 nm.

Our glass wafers, if not otherwise specified, are made of borosilicate glass.

#### Specifications

Common parameters for all wafers are diameter, thickness and surface (1- or 2-side polished). Fused silica wafers are made either of JGS1 or JGS2 material, for quartz wafers the crystal orientation needs to be defined. For silicon wafers, beside the crystal orientation (<100> or <111>) the doping (n- or p-type) as well as the resistivity (Ohm cm) are selection criteria.

#### Prime-, Test-, and Dummy Wafers

Silicon wafers usually come as "Prime-grade" or "Test-grade", latter mainly have a slightly broader particle specification. "Dummy-Wafers" neither fulfill Prime- nor Test-grade for different possible reasons (e. g. very broad or missing specification of one or several parameters, reclaim wafers, no particle specification) but might be a cheap alternative for e. g. resist coating tests or equipment start-up.

#### Our Silicon-, Quartz-, Fused Silica and Glass Wafers

Our frequently updated wafer stock list can be found here:

è www.microchemicals.com/products/wafers/waferlist.html

#### Further Products from our Portfolio

| Plating                                                            |                                                         |

|--------------------------------------------------------------------|---------------------------------------------------------|

| Plating solutions for e.g. gold, copper, nickel, tin or palladium: | è www.microchemicals.com/products/electroplating.html   |

| Solvents (MOS, VLSI, ULSI)                                         |                                                         |

| Acetone, isopropyl alcohol, MEK, DMSO, cyclopentanone, butylace    | etate, è www.microchemicals.com/products/solvents.html  |

| Acids and Bases (MOS, VLSI, ULSI)                                  |                                                         |

| Hydrochloric acid, sulphuric acid, nitric acid, KOH, TMAH,         | è www.microchemicals.com/products/etchants.html         |

| Etching Mixtures                                                   |                                                         |

| for e.g. chromium, gold, silicon, copper, titanium,                | è www.microchemicals.com/products/etching_mixtures.html |

#### **Further Information**

**Technical Data Sheets:**

Material Safety Data Sheets (MSDS):

www.microchemicals.com/downloads/product\_data\_sheets/photoresists.html

www.microchemicals.com/downloads/safety\_data\_sheets/msds\_links.html

#### **Our Photolithography Book and -Posters**

We see it as our main task to make you understand all aspects of microstructuring in an application-oriented way.

At present, we have implemented this claim with our book **Photolithography** on over 200 pages, as well as attractively designed DIN A0 posters for your office or laboratory.

We will gladly send both of these to you free of charge as our customer (if applicable, we charge shipping costs for non-European deliveries):

www.microchemicals.com/downloads/brochures.html

www.microchemicals.com/downloads/posters.html

Thank you for your interest!

#### **Disclaimer of Warranty & Trademarks**

All information, process descriptions, recipes, etc. contained in this book are compiled to the best of our knowledge. Nevertheless, we can not guarantee the correctness of the information. Particularly with regard to the formulations for chemical (etching) processes we assume no guarantee for the correct specification of the components, the mixing conditions, the preparation of the batches and their application.

The safe sequence of mixing components of a recipe usually does not correspond to the order of their listing. We do not warrant the full disclosure of any indications (among other things, health, work safety) of the risks associated with the preparation and use of the recipes and processes. The information in this book is based on our current knowledge and experience. Due to the abundance of possible influences in the processing and application of our products, they do not exempt the user from their own tests and trials. A guarantee of certain properties or suitability for a specific application can not be derived from our data. As a matter of principle, each employee is required to provide sufficient information in advance in the appropriate cases in order to prevent damage to persons and equipment. All descriptions, illustrations, data, conditions, weights, etc. can be changed without prior notice and do not constitute a contractually agreed product characteristics. The user of our products is responsible for any proprietary rights and existing laws.

Merck, Merck Performance Materials, AZ, the AZ logo, and the vibrant M are trademarks of Merck KGaA, Darmstadt, Germany

MicroChemicals GmbH Nicolaus-Otto-Str. 39 89079, Ulm Germany

Fon:

+49 (0)731 977 343 0

Fax:

+49 (0)731 977 343 29

e-Mail:

info@microchemicals.net

Internet:

www.microchemicals.net